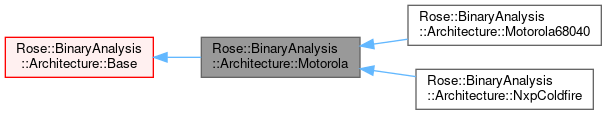

Description

Base class for Motorola processors.

Definition at line 12 of file Motorola.h.

#include <Rose/BinaryAnalysis/Architecture/Motorola.h>

Public Types | |

| using | Ptr = MotorolaPtr |

Public Types inherited from Rose::BinaryAnalysis::Architecture::Base Public Types inherited from Rose::BinaryAnalysis::Architecture::Base | |

| using | Ptr = BasePtr |

| Reference counting pointer. | |

| using | ConstPtr = BaseConstPtr |

| Reference counting pointer to const object. | |

Public Member Functions | |

| const CallingConvention::Dictionary & | callingConventions () const override |

| Property: Calling convention definitions. | |

| Sawyer::Container::Interval< size_t > | bytesPerInstruction () const override |

| Valid sizes for encoded machine instructions. | |

| Alignment | instructionAlignment () const override |

| Alignment for encoded machine instructions. | |

| std::string | instructionMnemonic (const SgAsmInstruction *) const override |

| Mnemonic for an instruction. | |

| std::string | instructionDescription (const SgAsmInstruction *) const override |

| Description for an instruction. | |

| bool | isUnknown (const SgAsmInstruction *) const override |

| Returns true if the instruction is the special "unknown" instruction. | |

| bool | terminatesBasicBlock (SgAsmInstruction *) const override |

| Determines whether the specified instruction normally terminates a basic block. | |

| bool | isFunctionCallFast (const std::vector< SgAsmInstruction * > &, Address *target, Address *ret) const override |

| Returns true if the specified basic block looks like a function call. | |

| bool | isFunctionCallSlow (const std::vector< SgAsmInstruction * > &, Address *target, Address *ret) const override |

| Returns true if the specified basic block looks like a function call. | |

| bool | isFunctionReturnFast (const std::vector< SgAsmInstruction * > &) const override |

| Returns true if the specified basic block looks like a function return. | |

| Sawyer::Optional< Address > | branchTarget (SgAsmInstruction *) const override |

| Obtains the virtual address for a branching instruction. | |

| AddressSet | getSuccessors (SgAsmInstruction *, bool &complete) const override |

| Control flow successors for a single instruction. | |

| AddressSet | getSuccessors (const std::vector< SgAsmInstruction * > &basicBlock, bool &complete, const MemoryMapPtr &initial_memory=MemoryMapPtr()) const override |

| Control flow successors for a basic block. | |

| Unparser::BasePtr | newUnparser () const override |

| Construct and return a new instruction unparser. | |

| virtual InstructionSemantics::BaseSemantics::DispatcherPtr | newInstructionDispatcher (const InstructionSemantics::BaseSemantics::RiscOperatorsPtr &) const override |

| Construct and return a new instruction dispatcher. | |

| std::vector< Partitioner2::FunctionPrologueMatcherPtr > | functionPrologueMatchers (const Partitioner2::EnginePtr &) const override |

| Instruction patterns matching function prologues. | |

| virtual std::vector< Partitioner2::BasicBlockCallbackPtr > | basicBlockCreationHooks (const Partitioner2::EnginePtr &) const override |

| Architecture-specific basic block callbacks for partitioning. | |

Public Member Functions inherited from Rose::BinaryAnalysis::Architecture::Base Public Member Functions inherited from Rose::BinaryAnalysis::Architecture::Base | |

| const std::string & | name () const |

| Property: Architecture definition name. | |

| ByteOrder::Endianness | byteOrder () const |

| Property: Byte order for memory. | |

| virtual RegisterDictionaryPtr | registerDictionary () const =0 |

| Property: Register dictionary. | |

| virtual RegisterDictionaryPtr | interruptDictionary () const |

| Property: Interrupt dictionary. | |

| virtual bool | matchesName (const std::string &) const |

| Tests whether this architecture matches a name. | |

| virtual bool | matchesHeader (SgAsmGenericHeader *) const |

| Tests whether this architecture matches a file header. | |

| virtual Disassembler::BasePtr | newInstructionDecoder () const =0 |

| Construct and return a new instruction decoder. | |

| bool | instructionsCanOverlap () const |

| Whether instructions can overlap in memory. | |

| virtual std::string | toString (const SgAsmExpression *) const |

| Unparse an expression to a string. | |

| virtual bool | isControlTransfer (const SgAsmInstruction *) const |

| Returns true if the specified instruction is a control transfer instruction. | |

| const Sawyer::Optional< size_t > & | registrationId () const |

| Property: Registration identification number. | |

| void | registrationId (const Sawyer::Optional< size_t > &) |

| Property: Registration identification number. | |

| size_t | bytesPerWord () const |

| Property: Word size. | |

| size_t | bitsPerWord () const |

| Property: Word size. | |

| virtual Unparser::BasePtr | newInstructionUnparser () const |

| Construct and return a new instruction unparser. | |

| virtual std::string | toString (const SgAsmInstruction *) const |

| Unparse an instruction to a string. | |

| virtual std::string | toStringNoAddr (const SgAsmInstruction *) const |

| Unparse an instruction to a string. | |

| virtual std::string | toStringNoColor (const SgAsmInstruction *) const |

| Unparse an instruction to a string. | |

| virtual std::string | toStringNoAddrNoColor (const SgAsmInstruction *) const |

| Unparse an instruction to a string. | |

| virtual bool | isFunctionReturnSlow (const std::vector< SgAsmInstruction * > &) const |

| Returns true if the specified basic block looks like a function return. | |

| AddressSet | getSuccessors (const std::vector< SgAsmInstruction * > &basicBlock, bool &complete) const |

| Control flow successors for a basic block. | |

Protected Member Functions | |

| Motorola (const std::string &name) | |

Protected Member Functions inherited from Rose::BinaryAnalysis::Architecture::Base Protected Member Functions inherited from Rose::BinaryAnalysis::Architecture::Base | |

| Base (const std::string &name, size_t bytesPerWord, ByteOrder::Endianness byteOrder) | |

| Ptr | ptr () |

| ConstPtr | constPtr () const |

| virtual Unparser::BasePtr | insnUnparser () const |

Additional Inherited Members | |

Protected Attributes inherited from Rose::BinaryAnalysis::Architecture::Base Protected Attributes inherited from Rose::BinaryAnalysis::Architecture::Base | |

| Sawyer::Cached< RegisterDictionaryPtr > | registerDictionary_ |

| Sawyer::Cached< RegisterDictionaryPtr > | interruptDictionary_ |

| Sawyer::Cached< CallingConvention::Dictionary > | callingConventions_ |

| Sawyer::Cached< Unparser::Base::Ptr > | insnToString_ |

| Sawyer::Cached< Unparser::Base::Ptr > | insnToStringNoAddr_ |

| Sawyer::Cached< Unparser::Base::Ptr > | insnToStringNoColor_ |

| Sawyer::Cached< Unparser::Base::Ptr > | insnToStringNoAddrNoColor_ |

Member Typedef Documentation

◆ Ptr

| using Rose::BinaryAnalysis::Architecture::Motorola::Ptr = MotorolaPtr |

Definition at line 14 of file Motorola.h.

Member Function Documentation

◆ callingConventions()

|

overridevirtual |

Property: Calling convention definitions.

Returns a list of calling convention definitions used by this architecture. Since definitions are generally not modified, it is permissible for this function to return the same definitions every time it's called. The list can be constructed on the first call.

The default implementation returns an empty list.

Thread safety: Thread safe.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

◆ bytesPerInstruction()

|

overridevirtual |

Valid sizes for encoded machine instructions.

Returns the range of valid sizes for encoded machine instructions. For instance, an x86 instruction can be from one to 15 bytes in length, but a PowerPC PPC32 instruction is always exactly 4 bytes.

Implements Rose::BinaryAnalysis::Architecture::Base.

◆ instructionAlignment()

|

overridevirtual |

Alignment for encoded machine instructions.

Implements Rose::BinaryAnalysis::Architecture::Base.

◆ instructionMnemonic()

|

overridevirtual |

Mnemonic for an instruction.

Returns the mnemonic for a particular instruction.

Thread safety: Thread safe.

Implements Rose::BinaryAnalysis::Architecture::Base.

◆ instructionDescription()

|

overridevirtual |

Description for an instruction.

Returns the description for a particular instruction. The description must be a single line with no leading or trailing white space, no line termination characters, and no non-printable characters. Most subclasses will just return a string based on the instruction mnemonic, such as "push a value onto the stack" for a PUSH instruction. The instruction argument must not be a null pointer and must be valid for this architecture.

The default implementation returns an empty string.

Thread safety: Thread safe.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

◆ isUnknown()

|

overridevirtual |

Returns true if the instruction is the special "unknown" instruction.

Each instruction architecture in ROSE defines an "unknown" instruction to be used when the disassembler is unable to create a real instruction. This can happen, for instance, if the bit pattern does not represent a valid instruction for the architecture. The instruction must not be a null pointer, and must be valid for this architecture.

Thread safety: Thread safe.

Implements Rose::BinaryAnalysis::Architecture::Base.

◆ terminatesBasicBlock()

|

overridevirtual |

Determines whether the specified instruction normally terminates a basic block.

The analysis generally only looks at the individual instruction and therefore is not very sophisticated. For instance, a conditional branch will always terminate a basic block by this method even if its condition is opaque. The instruction argument must not be a null pointer and must be valid for this architecture.

Thread safety: Thread safe.

Implements Rose::BinaryAnalysis::Architecture::Base.

◆ isFunctionCallFast()

|

overridevirtual |

Returns true if the specified basic block looks like a function call.

If the basic block looks like a function call then this method returns true. If (and only if) the target address is known (i.e., the address of the called function) then target is set to this address (otherwise target is unmodified). If the return address is known or can be guessed, then return_va is initialized to the return address, which is normally the fall-through address of the last instruction; otherwise the return_va is unmodified.

The "fast" and "slow" versions differ only in what kind of anlysis they do. The "fast" version typically looks only at instruction patterns while the slow version might incur more expense by looking at instruction semantics.

The base implementation of the fast method always returns false. The base implementation of the slow method just calls the fast method.

Thread safety: Thread safe.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

◆ isFunctionCallSlow()

|

overridevirtual |

Returns true if the specified basic block looks like a function call.

If the basic block looks like a function call then this method returns true. If (and only if) the target address is known (i.e., the address of the called function) then target is set to this address (otherwise target is unmodified). If the return address is known or can be guessed, then return_va is initialized to the return address, which is normally the fall-through address of the last instruction; otherwise the return_va is unmodified.

The "fast" and "slow" versions differ only in what kind of anlysis they do. The "fast" version typically looks only at instruction patterns while the slow version might incur more expense by looking at instruction semantics.

The base implementation of the fast method always returns false. The base implementation of the slow method just calls the fast method.

Thread safety: Thread safe.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

◆ isFunctionReturnFast()

|

overridevirtual |

Returns true if the specified basic block looks like a function return.

The "fast" and "slow" versions differ only in what kind of anlysis they do. The "fast" version typically looks only at instruction patterns while the slow version might incur more expense by looking at instruction semantics.

The base implementaiton of the fast method always returns false. The base implementation of the slow method just calls the fast method.

Thread safety: Thread safe.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

◆ branchTarget()

|

overridevirtual |

Obtains the virtual address for a branching instruction.

Returns the branch target address if the specified instruction is a branching instruction and the target is known; otherwise returns nothing.

The default implementation returns nothing.

Thread safety: Thread safe.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

◆ getSuccessors() [1/2]

|

overridevirtual |

Control flow successors for a single instruction.

The return value does not consider neighboring instructions, and therefore is quite naive. It returns only the information it can glean from this single instruction. If the returned set of virtual instructions is fully known then the complete argument will be set to true, otherwise false. The instruction must not be null, and must be valid for this architecture.

The default implementation always returns an empty set and clears complete.

Thread safety: Thread saafe.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

◆ getSuccessors() [2/2]

|

overridevirtual |

Control flow successors for a basic block.

The basicBlock argument is a vector of instructions that is assumed to be a basic block that is entered only at the first instruction and exits only at the last instruction. A memory map can supply initial values for the analysis' memory state. The return value is a set of control flow successor virtual addresses, and the complete argument return value indicates whether the returned set is known to be complete (aside from interrupts, faults, etc).

The default implementation calls the single-instruction version, so architecture-specific subclasses might want to override this to do something more sophisticated. However, if the basic block is empty then this function instead returns an empty set and sets complete to true.

Thread safety: Thread safe.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

◆ newUnparser()

|

overridevirtual |

Construct and return a new instruction unparser.

An unparser is responsible for generating pseudo assembly listings.

The newUnparser returns a default configured unparser suitable for unparsing instructions in the context of an assembly listing. The newInstructionUnparser returns a parser configured to show individual instructions showing only the instruction address, the instruction mnemonic, and the operands.

Example: The default instruction unparser uses color by default. If you want to turn off the color, you must create a new unparser, configure it to disable color, and then use it to unparse the instruction.

Thread safety: Thread safe.

Implements Rose::BinaryAnalysis::Architecture::Base.

◆ newInstructionDispatcher()

|

overridevirtual |

Construct and return a new instruction dispatcher.

The dispatcher knows the semantics for instructions, but not the low-level operators (arithmetic, memory I/O, etc), nor the domain (concrete, symbolic, etc) on which those operators operate. These other things are supplied by the argument, which also points to the states that are modified by executing the instructions.

The default implementation returns a null pointer, signifying that instruction semantics are not known.

Thread safety: Thread safe.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

◆ functionPrologueMatchers()

|

overridevirtual |

Instruction patterns matching function prologues.

Returns a list of matchers that match sequences of instructions that are often generated by compilers as part of instruction prologues.

The default implementation returns an empty list.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

◆ basicBlockCreationHooks()

|

overridevirtual |

Architecture-specific basic block callbacks for partitioning.

Returns a list of basic block callbacks used by the partitioner during disassembly.

The default implementation returns an empty list.

Reimplemented from Rose::BinaryAnalysis::Architecture::Base.

The documentation for this class was generated from the following file: