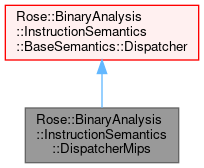

Description

Dispatches MIPS instructions through the semantics layer.

The instruction is lowered to a set of a few dozen operations that operate on values and states in a semantic domain.

Definition at line 31 of file DispatcherMips.h.

#include <Rose/BinaryAnalysis/InstructionSemantics/DispatcherMips.h>

Public Types | |

| using | Super = BaseSemantics::Dispatcher |

| Base type. | |

| using | Ptr = DispatcherMipsPtr |

| Shared-ownership pointer. | |

Public Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Public Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| using | Ptr = DispatcherPtr |

| Shared-ownership pointer. | |

Public Member Functions | |

| virtual BaseSemantics::DispatcherPtr | create (const BaseSemantics::RiscOperatorsPtr &) const override |

| Virtual constructor. | |

| virtual int | iprocKey (SgAsmInstruction *) const override |

| Given an instruction, return the InsnProcessor key that can be used as an index into the iproc_table. | |

| virtual BaseSemantics::SValuePtr | read (SgAsmExpression *, size_t valueNBits=0, size_t addrNBits=0) override |

| Reads an R-value expression. | |

Public Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Public Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| virtual void | processInstruction (SgAsmInstruction *insn) |

| Process a single instruction. | |

| virtual void | processDelaySlot (SgAsmInstruction *delayInsn) |

| Process a delay slot. | |

| virtual InsnProcessor * | iprocLookup (SgAsmInstruction *insn) |

| Lookup the processor for an instruction. | |

| virtual void | iprocReplace (SgAsmInstruction *insn, InsnProcessor *iproc) |

| Replace an instruction processor with another. | |

| virtual void | iprocSet (int key, InsnProcessor *iproc) |

| Set an iproc table entry to the specified value. | |

| virtual InsnProcessor * | iprocGet (int key) |

| Obtain an iproc table entry for the specified key. | |

| Architecture::BaseConstPtr | architecture () const |

| Property: Architecture. | |

| virtual StatePtr | currentState () const |

| Get a pointer to the state object. | |

| virtual SValuePtr | protoval () const |

| Return the prototypical value. | |

| virtual SgAsmInstruction * | currentInstruction () const |

| Returns the instruction that is being processed. | |

| virtual SValuePtr | number_ (size_t nbits, uint64_t number) const |

| Return a semantic value representing a number. | |

| RegisterDictionaryPtr | registerDictionary () const |

| Property: Register dictionary. | |

| virtual RegisterDescriptor | findRegister (const std::string ®name, size_t nbits=0, bool allowMissing=false) const |

| Lookup a register by name. | |

| size_t | addressWidth () const |

| Property: Width of memory addresses in bits. | |

| virtual RegisterDescriptor | instructionPointerRegister () const |

| Returns the instruction pointer register. | |

| virtual RegisterDescriptor | stackPointerRegister () const |

| Returns the stack pointer register. | |

| virtual RegisterDescriptor | stackFrameRegister () const |

| Returns the stack call frame register. | |

| virtual RegisterDescriptor | callReturnRegister () const |

| Returns the function call return address register. | |

| virtual void | initializeState (const StatePtr &) |

| Initialize the state. | |

| virtual void | advanceInstructionPointer (SgAsmInstruction *) |

| Update the instruction pointer register. | |

| virtual RegisterDescriptor | segmentRegister (SgAsmMemoryReferenceExpression *) |

| Returns a register descriptor for the segment part of a memory reference expression. | |

| virtual void | incrementRegisters (SgAsmExpression *) |

| Increment all auto-increment registers in the expression. | |

| virtual void | decrementRegisters (SgAsmExpression *) |

| Decrement all auto-decrement registers in the expression. | |

| virtual void | preUpdate (SgAsmExpression *, const BaseSemantics::SValuePtr &enabled) |

| Update registers for pre-add expressions. | |

| virtual void | postUpdate (SgAsmExpression *, const BaseSemantics::SValuePtr &enabled) |

| Update registers for post-add expressions. | |

| virtual SValuePtr | effectiveAddress (SgAsmExpression *, size_t nbits=0) |

| Returns a memory address by evaluating the address expression. | |

| virtual void | write (SgAsmExpression *, const SValuePtr &value, size_t addr_nbits=0) |

| Writes to an L-value expression. | |

| virtual RiscOperatorsPtr | operators () const |

| Property: RISC operators. | |

| virtual void | operators (const RiscOperatorsPtr &) |

| Property: RISC operators. | |

| virtual SValuePtr | undefined_ (size_t nbits) const |

| Return a new undefined semantic value. | |

| virtual SValuePtr | unspecified_ (size_t nbits) const |

| Return a new undefined semantic value. | |

| bool | autoResetInstructionPointer () const |

| Property: Reset instruction pointer register for each instruction. | |

| void | autoResetInstructionPointer (bool b) |

| Property: Reset instruction pointer register for each instruction. | |

Static Public Member Functions | |

| static Ptr | instance (const Architecture::BaseConstPtr &) |

| Construct a prototypical dispatcher. | |

| static Ptr | instance (const Architecture::BaseConstPtr &, const BaseSemantics::RiscOperatorsPtr &) |

| Constructor. | |

| static Ptr | promote (const BaseSemantics::DispatcherPtr &) |

| Dynamic cast to DispatcherMipsPtr with assertion. | |

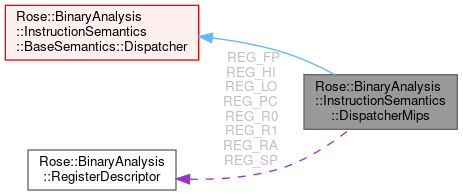

Public Attributes | |

| const RegisterDescriptor | REG_R0 |

| Cached register. | |

| const RegisterDescriptor | REG_R1 |

| Cached register. | |

| const RegisterDescriptor | REG_HI |

| Cached register. | |

| const RegisterDescriptor | REG_LO |

| Cached register. | |

| const RegisterDescriptor | REG_PC |

| Cached register. | |

| const RegisterDescriptor | REG_SP |

| Cached register. | |

| const RegisterDescriptor | REG_FP |

| Cached register. | |

| const RegisterDescriptor | REG_RA |

| Cached register. | |

| const RegisterDescriptor | REG_ZERO |

| Cached register. | |

Protected Member Functions | |

| DispatcherMips (const Architecture::BaseConstPtr &) | |

| DispatcherMips (const Architecture::BaseConstPtr &, const BaseSemantics::RiscOperatorsPtr &) | |

Protected Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Protected Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| Dispatcher (const Architecture::BaseConstPtr &) | |

| Dispatcher (const Architecture::BaseConstPtr &, const RiscOperatorsPtr &) | |

| virtual void | processCommon () |

Additional Inherited Members | |

Protected Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Protected Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| typedef std::vector< InsnProcessor * > | InsnProcessors |

Protected Attributes inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Protected Attributes inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| bool | autoResetInstructionPointer_ = true |

| Reset instruction pointer register for each instruction. | |

| InsnProcessors | iproc_table |

Member Typedef Documentation

◆ Super

Base type.

Definition at line 34 of file DispatcherMips.h.

◆ Ptr

Shared-ownership pointer.

Definition at line 37 of file DispatcherMips.h.

Member Function Documentation

◆ instance()

|

static |

Construct a prototypical dispatcher.

The only thing this dispatcher can be used for is to create another dispatcher with the virtual create method.

◆ create()

|

overridevirtual |

Virtual constructor.

Implements Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ iprocKey()

|

overridevirtual |

Given an instruction, return the InsnProcessor key that can be used as an index into the iproc_table.

Implements Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ read()

|

overridevirtual |

Reads an R-value expression.

The expression can be a constant, register reference, or memory reference. The width of the returned value is specified by the value_nbits argument, and if this argument is zero then the width of the expression type is used. The width of the address passed to lower-level memory access functions is specified by addr_nbits. If addr_nbits is zero then the natural width of the effective address is passed to lower level functions.

Reimplemented from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

Member Data Documentation

◆ REG_R0

| const RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips::REG_R0 |

Cached register.

This register is cached so that there are not so many calls to look up registers by name.

Definition at line 45 of file DispatcherMips.h.

◆ REG_R1

| const RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips::REG_R1 |

Cached register.

This register is cached so that there are not so many calls to look up registers by name.

Definition at line 45 of file DispatcherMips.h.

◆ REG_HI

| const RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips::REG_HI |

Cached register.

This register is cached so that there are not so many calls to look up registers by name.

Definition at line 45 of file DispatcherMips.h.

◆ REG_LO

| const RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips::REG_LO |

Cached register.

This register is cached so that there are not so many calls to look up registers by name.

Definition at line 45 of file DispatcherMips.h.

◆ REG_PC

| const RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips::REG_PC |

Cached register.

This register is cached so that there are not so many calls to look up registers by name.

Definition at line 45 of file DispatcherMips.h.

◆ REG_SP

| const RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips::REG_SP |

Cached register.

This register is cached so that there are not so many calls to look up registers by name.

Definition at line 45 of file DispatcherMips.h.

◆ REG_FP

| const RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips::REG_FP |

Cached register.

This register is cached so that there are not so many calls to look up registers by name.

Definition at line 45 of file DispatcherMips.h.

◆ REG_RA

| const RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips::REG_RA |

Cached register.

This register is cached so that there are not so many calls to look up registers by name.

Definition at line 45 of file DispatcherMips.h.

◆ REG_ZERO

| const RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips::REG_ZERO |

Cached register.

This register is cached so that there are not so many calls to look up registers by name.

Definition at line 45 of file DispatcherMips.h.

The documentation for this class was generated from the following file: