Description

Dispatches instructions through the RISC layer.

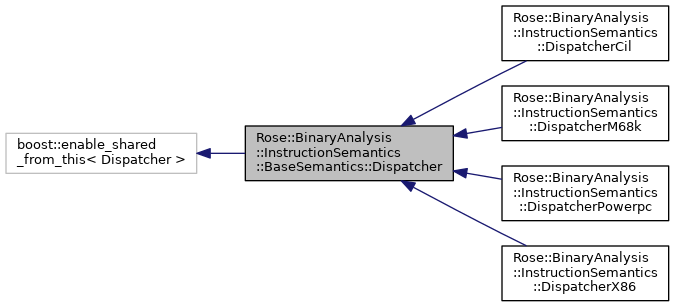

The dispatcher is the instruction semantics entity that translates a high-level architecture-dependent instruction into a sequence of RISC operators whose interface is defined by ROSE. These classes are the key in ROSE's ability to connect a variety of instruction set architectures to a variety of semantic domains.

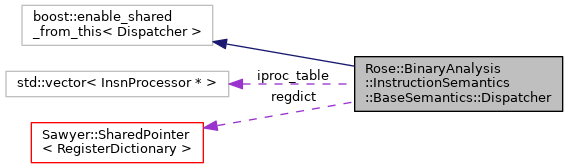

Each dispatcher contains a table indexed by the machine instruction "kind" (e.g., SgAsmMipsInstruction::get_kind()). The table stores functors derived from the abstract InsnProcessor class. (FIXME: The functors are not currently reference counted; they are owned by the dispatcher and deleted when the dispatcher is destroyed. [Robb Matzke 2013-03-04])

Dispatcher objects are allocated on the heap and reference counted. The BaseSemantics::Dispatcher is an abstract class that defines the interface. See the Rose::BinaryAnalysis::InstructionSemantics namespace for an overview of how the parts fit together.

Definition at line 46 of file Dispatcher.h.

#include <Rose/BinaryAnalysis/InstructionSemantics/BaseSemantics/Dispatcher.h>

Public Types | |

| using | Ptr = DispatcherPtr |

| Shared-ownership pointer. | |

Public Member Functions | |

| virtual DispatcherPtr | create (const RiscOperatorsPtr &ops) const =0 |

| Virtual constructor. | |

| virtual void | processInstruction (SgAsmInstruction *insn) |

| Process a single instruction. | |

| virtual void | processDelaySlot (SgAsmInstruction *delayInsn) |

| Process a delay slot. | |

| virtual InsnProcessor * | iprocLookup (SgAsmInstruction *insn) |

| Lookup the processor for an instruction. | |

| virtual void | iprocReplace (SgAsmInstruction *insn, InsnProcessor *iproc) |

| Replace an instruction processor with another. | |

| virtual int | iprocKey (SgAsmInstruction *) const =0 |

| Given an instruction, return the InsnProcessor key that can be used as an index into the iproc_table. | |

| virtual void | iprocSet (int key, InsnProcessor *iproc) |

| Set an iproc table entry to the specified value. | |

| virtual InsnProcessor * | iprocGet (int key) |

| Obtain an iproc table entry for the specified key. | |

| Architecture::BaseConstPtr | architecture () const |

| Property: Architecture. | |

| virtual StatePtr | currentState () const |

| Get a pointer to the state object. | |

| virtual SValuePtr | protoval () const |

| Return the prototypical value. | |

| virtual SgAsmInstruction * | currentInstruction () const |

| Returns the instruction that is being processed. | |

| virtual SValuePtr | number_ (size_t nbits, uint64_t number) const |

| Return a semantic value representing a number. | |

| RegisterDictionaryPtr | registerDictionary () const |

| Property: Register dictionary. | |

| virtual RegisterDescriptor | findRegister (const std::string ®name, size_t nbits=0, bool allowMissing=false) const |

| Lookup a register by name. | |

| size_t | addressWidth () const |

| Property: Width of memory addresses in bits. | |

| virtual RegisterDescriptor | instructionPointerRegister () const |

| Returns the instruction pointer register. | |

| virtual RegisterDescriptor | stackPointerRegister () const |

| Returns the stack pointer register. | |

| virtual RegisterDescriptor | stackFrameRegister () const |

| Returns the stack call frame register. | |

| virtual RegisterDescriptor | callReturnRegister () const |

| Returns the function call return address register. | |

| virtual void | initializeState (const StatePtr &) |

| Initialize the state. | |

| virtual void | advanceInstructionPointer (SgAsmInstruction *) |

| Update the instruction pointer register. | |

| virtual RegisterDescriptor | segmentRegister (SgAsmMemoryReferenceExpression *) |

| Returns a register descriptor for the segment part of a memory reference expression. | |

| virtual void | incrementRegisters (SgAsmExpression *) |

| Increment all auto-increment registers in the expression. | |

| virtual void | decrementRegisters (SgAsmExpression *) |

| Decrement all auto-decrement registers in the expression. | |

| virtual void | preUpdate (SgAsmExpression *, const BaseSemantics::SValuePtr &enabled) |

| Update registers for pre-add expressions. | |

| virtual void | postUpdate (SgAsmExpression *, const BaseSemantics::SValuePtr &enabled) |

| Update registers for post-add expressions. | |

| virtual SValuePtr | effectiveAddress (SgAsmExpression *, size_t nbits=0) |

| Returns a memory address by evaluating the address expression. | |

| virtual SValuePtr | read (SgAsmExpression *, size_t value_nbits=0, size_t addr_nbits=0) |

| Reads an R-value expression. | |

| virtual void | write (SgAsmExpression *, const SValuePtr &value, size_t addr_nbits=0) |

| Writes to an L-value expression. | |

| virtual RiscOperatorsPtr | operators () const |

| Property: RISC operators. | |

| virtual void | operators (const RiscOperatorsPtr &) |

| Property: RISC operators. | |

| virtual SValuePtr | undefined_ (size_t nbits) const |

| Return a new undefined semantic value. | |

| virtual SValuePtr | unspecified_ (size_t nbits) const |

| Return a new undefined semantic value. | |

| bool | autoResetInstructionPointer () const |

| Property: Reset instruction pointer register for each instruction. | |

| void | autoResetInstructionPointer (bool b) |

| Property: Reset instruction pointer register for each instruction. | |

Protected Types | |

| typedef std::vector< InsnProcessor * > | InsnProcessors |

Protected Member Functions | |

| Dispatcher (const Architecture::BaseConstPtr &) | |

| Dispatcher (const Architecture::BaseConstPtr &, const RiscOperatorsPtr &) | |

| virtual void | processCommon () |

Protected Attributes | |

| bool | autoResetInstructionPointer_ = true |

| Reset instruction pointer register for each instruction. | |

| InsnProcessors | iproc_table |

Member Typedef Documentation

◆ Ptr

Shared-ownership pointer.

Definition at line 49 of file Dispatcher.h.

◆ InsnProcessors

|

protected |

Definition at line 60 of file Dispatcher.h.

Member Function Documentation

◆ create()

|

pure virtual |

Virtual constructor.

Implemented in Rose::BinaryAnalysis::InstructionSemantics::DispatcherCil, Rose::BinaryAnalysis::InstructionSemantics::DispatcherM68k, Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips, Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc, and Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86.

◆ processInstruction()

|

virtual |

Process a single instruction.

This is the function that most users will call.

◆ processDelaySlot()

|

virtual |

Process a delay slot.

This is called when one instruction must temporarily interrupt its own processing to process some other instruction. It can be called recursively as often as needed, such as on architectures where there are multiple delay slots for some instructions. Users don't normally call this–it's intended to be called by the instruction semantics processing layers.

◆ iprocLookup()

|

virtual |

Lookup the processor for an instruction.

Looks up the functor that has been registered to process the given instruction. Returns the null pointer if the instruction cannot be processed. Instruction processor objects are managed by the caller; the instruction itself is only used for the duration of this call.

◆ iprocReplace()

|

virtual |

Replace an instruction processor with another.

The processor for the specified instruction is replaced with the specified processor, which may be the null pointer. Instruction processor objects are managed by the caller; the instruction itself is only used for the duration of this call.

◆ iprocKey()

|

pure virtual |

Given an instruction, return the InsnProcessor key that can be used as an index into the iproc_table.

Implemented in Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips, Rose::BinaryAnalysis::InstructionSemantics::DispatcherCil, Rose::BinaryAnalysis::InstructionSemantics::DispatcherM68k, Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc, and Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86.

◆ iprocSet()

|

virtual |

Set an iproc table entry to the specified value.

The iproc object will become owned by this dispatcher and deleted when this dispatcher is destroyed.

◆ architecture()

| Architecture::BaseConstPtr Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher::architecture | ( | ) | const |

Property: Architecture.

Non-null pointer to architecture-specific information.

◆ operators() [1/2]

|

virtual |

Property: RISC operators.

The RISC operators also contain the current and initial state on which they operate.

◆ operators() [2/2]

|

virtual |

Property: RISC operators.

The RISC operators also contain the current and initial state on which they operate.

◆ currentState()

|

virtual |

Get a pointer to the state object.

The state is stored in the RISC operators object, so this is just here for convenience.

◆ protoval()

|

virtual |

Return the prototypical value.

The prototypical value comes from the RISC operators object.

◆ currentInstruction()

|

virtual |

Returns the instruction that is being processed.

The instruction comes from the currentInstruction method of the RiscOperators object.

◆ registerDictionary()

| RegisterDictionaryPtr Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher::registerDictionary | ( | ) | const |

Property: Register dictionary.

The register dictionary translates register descriptors to names and vice versa and provides descriptors for common registers such as instruction and stack pointer registers.

This function is simply a wrapper that obtains the register dictionary from the architecture.

◆ findRegister()

|

virtual |

Lookup a register by name.

This dispatcher's register dictionary is consulted and the specified register is located by name. If a bit width is specified (nbits) then it must match the size of register that was found. If a valid register cannot be found then either an exception is thrown or an invalid register is returned depending on whether allowMissing is false or true, respectively.

◆ addressWidth()

| size_t Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher::addressWidth | ( | ) | const |

Property: Width of memory addresses in bits.

This property defines the width of memory addresses. All memory reads and writes (and any other defined memory operations) should pass address expressions that are this width.

◆ instructionPointerRegister()

|

virtual |

Returns the instruction pointer register.

Reimplemented in Rose::BinaryAnalysis::InstructionSemantics::DispatcherCil, Rose::BinaryAnalysis::InstructionSemantics::DispatcherM68k, Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc, and Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86.

◆ stackPointerRegister()

|

virtual |

Returns the stack pointer register.

Reimplemented in Rose::BinaryAnalysis::InstructionSemantics::DispatcherCil, Rose::BinaryAnalysis::InstructionSemantics::DispatcherM68k, and Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86.

◆ stackFrameRegister()

|

virtual |

Returns the stack call frame register.

Reimplemented in Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86.

◆ callReturnRegister()

|

virtual |

Returns the function call return address register.

Reimplemented in Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc.

◆ autoResetInstructionPointer() [1/2]

|

inline |

Property: Reset instruction pointer register for each instruction.

If this property is set, then each time an instruction is processed, the first thing that happens is that the instruction pointer register is reset to the concrete address of the instruction.

Definition at line 241 of file Dispatcher.h.

References autoResetInstructionPointer_.

◆ autoResetInstructionPointer() [2/2]

|

inline |

Property: Reset instruction pointer register for each instruction.

If this property is set, then each time an instruction is processed, the first thing that happens is that the instruction pointer register is reset to the concrete address of the instruction.

Definition at line 242 of file Dispatcher.h.

References autoResetInstructionPointer_.

◆ initializeState()

|

virtual |

Initialize the state.

Some architectures benefit from having their initial state initialized in a certain way. For instance, on x86/amd64 the segment registers CS, DS, and SS typically refer to the entire machine memory and can be initialized to have a zero base address.

Reimplemented in Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86.

◆ advanceInstructionPointer()

|

virtual |

Update the instruction pointer register.

Causes the instruction pointer register to point to the address following the specified instruction. Since every instruction has a concrete address, we could simply set the instruction pointer to that concrete address. However, some analyses depend on having an instruction pointer value that's built up by processing one instruction after another. Therefore, if we can recognize the register state implementation and determine that the instruction pointer registers' value is already stored, we'll increment that value, which might result in a concrete value depending on the semantic domain. Otherwise we just explicitly assign a new concrete value to that register.

◆ segmentRegister()

|

virtual |

Returns a register descriptor for the segment part of a memory reference expression.

Many architectures don't use segment registers (they have a flat virtual address space), in which case the returned register descriptor's is_valid() method returns false.

◆ incrementRegisters()

|

virtual |

Increment all auto-increment registers in the expression.

This method traverses the expression and increments each the register of each register reference expression that has a positive adjustment value. If the same register is encountered multiple times then it is incremented multiple times.

◆ decrementRegisters()

|

virtual |

Decrement all auto-decrement registers in the expression.

This method traverses the expression and increments each the register of each register reference expression that has a negative adjustment value. If the same register is encountered multiple times then it is decremented multiple times.

◆ preUpdate()

|

virtual |

Update registers for pre-add expressions.

For each SgAsmBinaryAddPreupdate, add the lhs and rhs operands and assign the sum to the lhs, which must be a register reference expression.

◆ postUpdate()

|

virtual |

Update registers for post-add expressions.

For each SgAsmBinaryAddPostupdate, add the lhs and rhs operands and assign the sum to the lhs, which must be a register reference expression.

◆ effectiveAddress()

|

virtual |

Returns a memory address by evaluating the address expression.

The address expression can be either a constant or an expression containing operators and constants. If nbits is non-zero then the result is sign extended or truncated to the specified width, otherwise the returned SValue is the natural width of the expression.

◆ read()

|

virtual |

Reads an R-value expression.

The expression can be a constant, register reference, or memory reference. The width of the returned value is specified by the value_nbits argument, and if this argument is zero then the width of the expression type is used. The width of the address passed to lower-level memory access functions is specified by addr_nbits. If addr_nbits is zero then the natural width of the effective address is passed to lower level functions.

Reimplemented in Rose::BinaryAnalysis::InstructionSemantics::DispatcherCil, Rose::BinaryAnalysis::InstructionSemantics::DispatcherM68k, and Rose::BinaryAnalysis::InstructionSemantics::DispatcherMips.

◆ write()

|

virtual |

Writes to an L-value expression.

The expression can be a register or memory reference. The width of the address passed to lower-level memory access functions is specified by addr_nbits. If addr_nbits is zero then the natural width of the effective address is passed to lower level functions.

Reimplemented in Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86.

Member Data Documentation

◆ autoResetInstructionPointer_

|

protected |

Reset instruction pointer register for each instruction.

Definition at line 56 of file Dispatcher.h.

Referenced by autoResetInstructionPointer(), and autoResetInstructionPointer().

◆ iproc_table

|

protected |

Definition at line 61 of file Dispatcher.h.

The documentation for this class was generated from the following file: