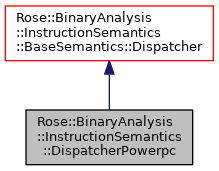

Description

Definition at line 30 of file DispatcherPowerpc.h.

Public Types | |

| using | Super = BaseSemantics::Dispatcher |

| Base type. | |

| using | Ptr = DispatcherPowerpcPtr |

| Shared-ownership pointer. | |

Public Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Public Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| using | Ptr = DispatcherPtr |

| Shared-ownership pointer. | |

Public Member Functions | |

| virtual BaseSemantics::DispatcherPtr | create (const BaseSemantics::RiscOperatorsPtr &) const override |

| Virtual constructor. | |

| virtual RegisterDescriptor | instructionPointerRegister () const override |

| Returns the instruction pointer register. | |

| virtual RegisterDescriptor | callReturnRegister () const override |

| Returns the function call return address register. | |

| virtual int | iprocKey (SgAsmInstruction *insn_) const override |

| Given an instruction, return the InsnProcessor key that can be used as an index into the iproc_table. | |

| void | setXerOverflow (const BaseSemantics::SValuePtr &hadOverflow) |

| Set the XER OV and SO bits as specified. | |

| virtual void | updateCr0 (const BaseSemantics::SValuePtr &result) |

| Write status flags for result. | |

| BaseSemantics::SValuePtr | readAndUpdate (BaseSemantics::RiscOperators *, SgAsmExpression *, size_t valueNBits) |

| Reads from a memory address and updates a register with the effective address that was read. | |

| void | writeAndUpdate (BaseSemantics::RiscOperators *, SgAsmExpression *destination, const BaseSemantics::SValuePtr &value) |

| Writes a value to a memory address and updates a register with the effective address to which the value was written. | |

Public Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Public Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| virtual void | processInstruction (SgAsmInstruction *insn) |

| Process a single instruction. | |

| virtual void | processDelaySlot (SgAsmInstruction *delayInsn) |

| Process a delay slot. | |

| virtual InsnProcessor * | iprocLookup (SgAsmInstruction *insn) |

| Lookup the processor for an instruction. | |

| virtual void | iprocReplace (SgAsmInstruction *insn, InsnProcessor *iproc) |

| Replace an instruction processor with another. | |

| virtual void | iprocSet (int key, InsnProcessor *iproc) |

| Set an iproc table entry to the specified value. | |

| virtual InsnProcessor * | iprocGet (int key) |

| Obtain an iproc table entry for the specified key. | |

| Architecture::BaseConstPtr | architecture () const |

| Property: Architecture. | |

| virtual StatePtr | currentState () const |

| Get a pointer to the state object. | |

| virtual SValuePtr | protoval () const |

| Return the prototypical value. | |

| virtual SgAsmInstruction * | currentInstruction () const |

| Returns the instruction that is being processed. | |

| virtual SValuePtr | number_ (size_t nbits, uint64_t number) const |

| Return a semantic value representing a number. | |

| RegisterDictionaryPtr | registerDictionary () const |

| Property: Register dictionary. | |

| virtual RegisterDescriptor | findRegister (const std::string ®name, size_t nbits=0, bool allowMissing=false) const |

| Lookup a register by name. | |

| size_t | addressWidth () const |

| Property: Width of memory addresses in bits. | |

| virtual RegisterDescriptor | stackPointerRegister () const |

| Returns the stack pointer register. | |

| virtual RegisterDescriptor | stackFrameRegister () const |

| Returns the stack call frame register. | |

| virtual void | initializeState (const StatePtr &) |

| Initialize the state. | |

| virtual void | advanceInstructionPointer (SgAsmInstruction *) |

| Update the instruction pointer register. | |

| virtual RegisterDescriptor | segmentRegister (SgAsmMemoryReferenceExpression *) |

| Returns a register descriptor for the segment part of a memory reference expression. | |

| virtual void | incrementRegisters (SgAsmExpression *) |

| Increment all auto-increment registers in the expression. | |

| virtual void | decrementRegisters (SgAsmExpression *) |

| Decrement all auto-decrement registers in the expression. | |

| virtual void | preUpdate (SgAsmExpression *, const BaseSemantics::SValuePtr &enabled) |

| Update registers for pre-add expressions. | |

| virtual void | postUpdate (SgAsmExpression *, const BaseSemantics::SValuePtr &enabled) |

| Update registers for post-add expressions. | |

| virtual SValuePtr | effectiveAddress (SgAsmExpression *, size_t nbits=0) |

| Returns a memory address by evaluating the address expression. | |

| virtual SValuePtr | read (SgAsmExpression *, size_t value_nbits=0, size_t addr_nbits=0) |

| Reads an R-value expression. | |

| virtual void | write (SgAsmExpression *, const SValuePtr &value, size_t addr_nbits=0) |

| Writes to an L-value expression. | |

| virtual RiscOperatorsPtr | operators () const |

| Property: RISC operators. | |

| virtual void | operators (const RiscOperatorsPtr &) |

| Property: RISC operators. | |

| virtual SValuePtr | undefined_ (size_t nbits) const |

| Return a new undefined semantic value. | |

| virtual SValuePtr | unspecified_ (size_t nbits) const |

| Return a new undefined semantic value. | |

| bool | autoResetInstructionPointer () const |

| Property: Reset instruction pointer register for each instruction. | |

| void | autoResetInstructionPointer (bool b) |

| Property: Reset instruction pointer register for each instruction. | |

Static Public Member Functions | |

| static DispatcherPowerpcPtr | instance (const Architecture::BaseConstPtr &) |

| Construct a prototypical dispatcher. | |

| static DispatcherPowerpcPtr | instance (const Architecture::BaseConstPtr &, const BaseSemantics::RiscOperatorsPtr &) |

| Constructor. | |

| static DispatcherPowerpcPtr | promote (const BaseSemantics::DispatcherPtr &) |

| Dynamic cast to a DispatcherPowerpcPtr with assertion. | |

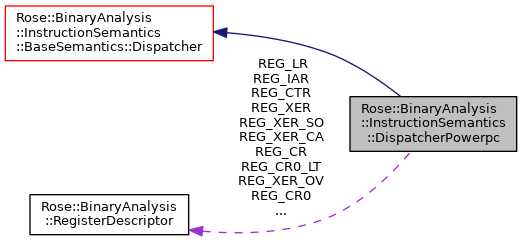

Public Attributes | |

| RegisterDescriptor | REG_IAR |

| Cached register. | |

| RegisterDescriptor | REG_LR |

| Cached register. | |

| RegisterDescriptor | REG_XER |

| Cached register. | |

| RegisterDescriptor | REG_XER_CA |

| Cached register. | |

| RegisterDescriptor | REG_XER_OV |

| Cached register. | |

| RegisterDescriptor | REG_XER_SO |

| Cached register. | |

| RegisterDescriptor | REG_CTR |

| Cached register. | |

| RegisterDescriptor | REG_CR |

| Cached register. | |

| RegisterDescriptor | REG_CR0 |

| Cached register. | |

| RegisterDescriptor | REG_CR0_LT |

| Cached register. | |

Protected Member Functions | |

| DispatcherPowerpc (const Architecture::BaseConstPtr &) | |

| DispatcherPowerpc (const Architecture::BaseConstPtr &, const BaseSemantics::RiscOperatorsPtr &) | |

Protected Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Protected Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| Dispatcher (const Architecture::BaseConstPtr &) | |

| Dispatcher (const Architecture::BaseConstPtr &, const RiscOperatorsPtr &) | |

| virtual void | processCommon () |

Additional Inherited Members | |

Protected Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Protected Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| typedef std::vector< InsnProcessor * > | InsnProcessors |

Protected Attributes inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Protected Attributes inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| bool | autoResetInstructionPointer_ = true |

| Reset instruction pointer register for each instruction. | |

| InsnProcessors | iproc_table |

Member Typedef Documentation

◆ Super

| using Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::Super = BaseSemantics::Dispatcher |

Base type.

Definition at line 33 of file DispatcherPowerpc.h.

◆ Ptr

Shared-ownership pointer.

Definition at line 36 of file DispatcherPowerpc.h.

Member Function Documentation

◆ instance()

|

static |

Construct a prototypical dispatcher.

The only thing this dispatcher can be used for is to create another dispatcher with the virtual create method.

◆ create()

|

overridevirtual |

Virtual constructor.

Implements Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ instructionPointerRegister()

|

overridevirtual |

Returns the instruction pointer register.

Reimplemented from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ callReturnRegister()

|

overridevirtual |

Returns the function call return address register.

Reimplemented from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ iprocKey()

|

overridevirtual |

Given an instruction, return the InsnProcessor key that can be used as an index into the iproc_table.

Implements Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ setXerOverflow()

| void Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::setXerOverflow | ( | const BaseSemantics::SValuePtr & | hadOverflow | ) |

◆ readAndUpdate()

| BaseSemantics::SValuePtr Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::readAndUpdate | ( | BaseSemantics::RiscOperators * | , |

| SgAsmExpression * | , | ||

| size_t | valueNBits | ||

| ) |

Reads from a memory address and updates a register with the effective address that was read.

The address expression must be a binary add operation whose first argument is a register, and it is this register that gets updated.

◆ writeAndUpdate()

| void Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::writeAndUpdate | ( | BaseSemantics::RiscOperators * | , |

| SgAsmExpression * | destination, | ||

| const BaseSemantics::SValuePtr & | value | ||

| ) |

Writes a value to a memory address and updates a register with the effective address to which the value was written.

The address expression must be a binary add operation whose first argument is a register, and it is this register that gets updated.

Member Data Documentation

◆ REG_IAR

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::REG_IAR |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Definition at line 44 of file DispatcherPowerpc.h.

◆ REG_LR

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::REG_LR |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Definition at line 44 of file DispatcherPowerpc.h.

◆ REG_XER

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::REG_XER |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Definition at line 44 of file DispatcherPowerpc.h.

◆ REG_XER_CA

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::REG_XER_CA |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Definition at line 44 of file DispatcherPowerpc.h.

◆ REG_XER_OV

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::REG_XER_OV |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Definition at line 44 of file DispatcherPowerpc.h.

◆ REG_XER_SO

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::REG_XER_SO |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Definition at line 44 of file DispatcherPowerpc.h.

◆ REG_CTR

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::REG_CTR |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Definition at line 44 of file DispatcherPowerpc.h.

◆ REG_CR

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::REG_CR |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Definition at line 45 of file DispatcherPowerpc.h.

◆ REG_CR0

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::REG_CR0 |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Definition at line 45 of file DispatcherPowerpc.h.

◆ REG_CR0_LT

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherPowerpc::REG_CR0_LT |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Definition at line 45 of file DispatcherPowerpc.h.

The documentation for this class was generated from the following file: