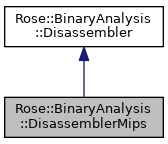

Description

Definition at line 14 of file DisassemblerMips.h.

Classes | |

| class | Mips32 |

| Interface for disassembling a single instruction. More... | |

Public Member Functions | |

| DisassemblerMips (ByteOrder::Endianness sex=ByteOrder::ORDER_MSB) | |

| Create a MIPS disassembler. More... | |

| virtual DisassemblerMips * | clone () const override |

| Creates a new copy of a disassembler. More... | |

| virtual bool | canDisassemble (SgAsmGenericHeader *) const override |

| Predicate determining the suitability of a disassembler for a specific file header. More... | |

| virtual SgAsmInstruction * | disassembleOne (const MemoryMap::Ptr &, rose_addr_t start_va, AddressSet *successors=NULL) override |

| This is the lowest level disassembly function and is implemented in the architecture-specific subclasses. More... | |

| virtual SgAsmInstruction * | makeUnknownInstruction (const Disassembler::Exception &) override |

| Makes an unknown instruction from an exception. More... | |

| SgAsmMipsInstruction * | makeUnknownInstruction (rose_addr_t insn_va, unsigned opcode) const |

| virtual Unparser::BasePtr | unparser () const override |

| Unparser. More... | |

| Mips32 * | find_idis (rose_addr_t insn_va, unsigned insn_bits) const |

| Find an instruction-specific disassembler. More... | |

| void | insert_idis (Mips32 *, bool replace=false) |

| Insert an instruction-specific disassembler. More... | |

| SgAsmMipsInstruction * | disassemble_insn (rose_addr_t insn_va, unsigned insn_bits) const |

| Disassemble a single instruction. More... | |

| SgAsmMipsInstruction * | makeInstruction (rose_addr_t insn_va, MipsInstructionKind, const std::string &mnemonic, SgAsmExpression *arg1=NULL, SgAsmExpression *arg2=NULL, SgAsmExpression *arg3=NULL, SgAsmExpression *arg4=NULL) const |

| Create a new instruction. More... | |

| SgAsmRegisterReferenceExpression * | makeRegister (rose_addr_t insn_va, unsigned regnum) const |

| Create a new general purpose register reference expression. More... | |

| SgAsmRegisterReferenceExpression * | makeFpRegister (rose_addr_t insn_va, unsigned regnum) const |

| Create a new floating point register reference expression. More... | |

| SgAsmRegisterReferenceExpression * | makeCp0Register (rose_addr_t insn_va, unsigned regnum, unsigned sel) const |

| Create a new register reference for Coprocessor 0. More... | |

| SgAsmRegisterReferenceExpression * | makeCp2Register (unsigned regnum) const |

| Create a new register reference for Coprocessor 2. More... | |

| SgAsmRegisterReferenceExpression * | makeFpccRegister (rose_addr_t insn_va, unsigned cc) const |

| Create a new floating point condition flag register reference expression. More... | |

| SgAsmRegisterReferenceExpression * | makeCp2ccRegister (unsigned cc) const |

| Create a new register reference for a COP2 condition code. More... | |

| SgAsmRegisterReferenceExpression * | makeHwRegister (unsigned regnum) const |

| Create a new register reference for a hardware register. More... | |

| SgAsmRegisterReferenceExpression * | makeShadowRegister (rose_addr_t insn_va, unsigned regnum) const |

| Create a new register reference for a shadow GPR. More... | |

| SgAsmIntegerValueExpression * | makeImmediate8 (unsigned value, size_t bit_offset, size_t nbits) const |

| Create a new 8-bit value expression from an 8-bit value. More... | |

| SgAsmIntegerValueExpression * | makeImmediate16 (unsigned value, size_t bit_offset, size_t nbits) const |

| Create a new 16-bit value expression from a 16-bit value. More... | |

| SgAsmIntegerValueExpression * | makeImmediate32 (unsigned value, size_t bit_offset, size_t nbits) const |

| Create a new 32-bit value expression from a 32-bit value. More... | |

| SgAsmIntegerValueExpression * | makeBranchTargetRelative (rose_addr_t insn_va, unsigned offset16, size_t bit_offset, size_t nbits) const |

| Create a 32-bit PC-relative branch target address from a 16-bit offset. More... | |

| SgAsmIntegerValueExpression * | makeBranchTargetAbsolute (rose_addr_t insn_va, unsigned insn_index, size_t bit_offset, size_t nbits) const |

| Create a 32-bit branch address from an instruction index value. More... | |

| SgAsmBinaryAdd * | makeRegisterOffset (rose_addr_t insn_va, unsigned gprnum, unsigned offset16) const |

| Build an expression for an offset from a register. More... | |

| SgAsmBinaryAdd * | makeRegisterIndexed (rose_addr_t insn_va, unsigned base_gprnum, unsigned index_gprnum) const |

| Build a register index expression. More... | |

| SgAsmMemoryReferenceExpression * | makeMemoryReference (SgAsmExpression *addr, SgAsmType *type) const |

| Build a memory reference expression. More... | |

Public Member Functions inherited from Rose::BinaryAnalysis::Disassembler Public Member Functions inherited from Rose::BinaryAnalysis::Disassembler | |

| size_t | instructionAlignment () const |

| Property: Instruction alignment requirement. More... | |

| virtual RegisterDescriptor | instructionPointerRegister () const |

| Returns the register that points to instructions. More... | |

| virtual RegisterDescriptor | stackPointerRegister () const |

| Returns the register that points to the stack. More... | |

| virtual RegisterDescriptor | stackFrameRegister () const |

| Returns the register that ponts to the stack frame. More... | |

| virtual RegisterDescriptor | stackSegmentRegister () const |

| Returns the segment register for accessing the stack. More... | |

| virtual RegisterDescriptor | callReturnRegister () const |

| Returns the register that holds the return address for a function. More... | |

| const Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::DispatcherPtr & | dispatcher () const |

| Return an instruction semantics dispatcher if possible. More... | |

| SgAsmInstruction * | disassembleOne (const unsigned char *buf, rose_addr_t buf_va, size_t buf_size, rose_addr_t start_va, AddressSet *successors=NULL) |

| Similar in functionality to the disassembleOne method that takes a MemoryMap argument, except the content buffer is mapped 1:1 to virtual memory beginning at the specified address. More... | |

| void | mark_referenced_instructions (SgAsmInterpretation *, const MemoryMap::Ptr &, const InstructionMap &) |

| Marks parts of the file that correspond to instructions as having been referenced. More... | |

| AddressSet | get_block_successors (const InstructionMap &, bool &complete) |

| Calculates the successor addresses of a basic block and adds them to a successors set. More... | |

| const std::string & | name () const |

| Property: Name by which disassembler is registered. | |

| void | name (const std::string &s) |

| Property: Name by which disassembler is registered. | |

| ByteOrder::Endianness | byteOrder () const |

| Property: Byte order of instructions in memory. | |

| void | byteOrder (ByteOrder::Endianness sex) |

| Property: Byte order of instructions in memory. | |

| size_t | wordSizeBytes () const |

| Property: Basic word size in bytes. | |

| void | wordSizeBytes (size_t nbytes) |

| Property: Basic word size in bytes. | |

| void | registerDictionary (const RegisterDictionary *rdict) |

| Properties: Register dictionary. More... | |

| const RegisterDictionary * | registerDictionary () const |

| Properties: Register dictionary. More... | |

| const CallingConvention::Dictionary & | callingConventions () const |

| Property: Calling convention dictionary. More... | |

| CallingConvention::Dictionary & | callingConventions () |

| Properties: Register dictionary. More... | |

| void | callingConventions (const CallingConvention::Dictionary &d) |

| Properties: Register dictionary. More... | |

Protected Member Functions | |

| void | init (ByteOrder::Endianness) |

Protected Attributes | |

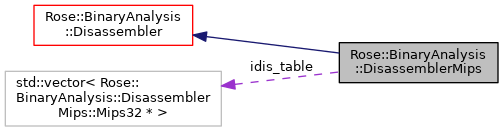

| std::vector< Mips32 * > | idis_table |

| Table of instruction-specific disassemblers. More... | |

Protected Attributes inherited from Rose::BinaryAnalysis::Disassembler Protected Attributes inherited from Rose::BinaryAnalysis::Disassembler | |

| const RegisterDictionary * | p_registers |

| Description of registers available for this platform. More... | |

| RegisterDescriptor | REG_IP |

| RegisterDescriptor | REG_SP |

| RegisterDescriptor | REG_SS |

| RegisterDescriptor | REG_SF |

| RegisterDescriptor | REG_LINK |

| Register descriptors initialized during construction. More... | |

| ByteOrder::Endianness | p_byteOrder |

| Byte order of instructions in memory. More... | |

| size_t | p_wordSizeBytes |

| Basic word size in bytes. More... | |

| std::string | p_name |

| Name by which this dissassembler is registered. More... | |

| size_t | instructionAlignment_ |

| Positive alignment constraint for instruction addresses. More... | |

| InstructionSemantics::BaseSemantics::DispatcherPtr | p_proto_dispatcher |

| Prototypical dispatcher for creating real dispatchers. | |

Additional Inherited Members | |

Public Types inherited from Rose::BinaryAnalysis::Disassembler Public Types inherited from Rose::BinaryAnalysis::Disassembler | |

| typedef Map< rose_addr_t, SgAsmInstruction * > | InstructionMap |

| The InstructionMap is a mapping from (absolute) virtual address to disassembled instruction. More... | |

Static Public Member Functions inherited from Rose::BinaryAnalysis::Disassembler Static Public Member Functions inherited from Rose::BinaryAnalysis::Disassembler | |

| static void | registerSubclass (Disassembler *) |

| Register a disassembler instance. More... | |

| static Disassembler * | lookup (SgAsmGenericHeader *) |

| Finds a suitable disassembler. More... | |

| static std::vector< std::string > | isaNames () |

| List of names recognized by lookup. More... | |

| static Disassembler * | lookup (SgAsmInterpretation *) |

| Finds a suitable disassembler. More... | |

| static Disassembler * | lookup (const std::string &) |

| Finds a suitable disassembler. More... | |

| static void | initDiagnostics () |

| Initializes and registers disassembler diagnostic streams. More... | |

Static Public Attributes inherited from Rose::BinaryAnalysis::Disassembler Static Public Attributes inherited from Rose::BinaryAnalysis::Disassembler | |

| static Sawyer::Message::Facility | mlog |

| Disassembler diagnostic streams. More... | |

Static Protected Attributes inherited from Rose::BinaryAnalysis::Disassembler Static Protected Attributes inherited from Rose::BinaryAnalysis::Disassembler | |

| static std::vector< Disassembler * > | disassemblers |

| List of disassembler subclasses. More... | |

Constructor & Destructor Documentation

|

inlineexplicit |

Create a MIPS disassembler.

MIPS executables can be big- or little-endian.

Definition at line 19 of file DisassemblerMips.h.

Referenced by clone().

Member Function Documentation

|

inlineoverridevirtual |

Creates a new copy of a disassembler.

The new copy has all the same settings as the original.

Thread safety: The thread safety of this virtual method depends on the implementation in the subclass.

Implements Rose::BinaryAnalysis::Disassembler.

Definition at line 21 of file DisassemblerMips.h.

References DisassemblerMips().

|

overridevirtual |

Predicate determining the suitability of a disassembler for a specific file header.

If this disassembler is capable of disassembling machine code described by the specified file header, then this predicate returns true, otherwise it returns false.

Thread safety: The thread safety of this virtual method depends on the implementation in the subclass.

Implements Rose::BinaryAnalysis::Disassembler.

|

overridevirtual |

This is the lowest level disassembly function and is implemented in the architecture-specific subclasses.

It disassembles one instruction at the specified virtual address. The map is a mapping from virtual addresses to buffer and enables instructions to span file segments that are mapped contiguously in virtual memory by the loader but which might not be contiguous in the file. The instruction's successor virtual addresses are added to the optional successor set (note that successors of an individual instruction can also be obtained via SgAsmInstruction::getSuccessors). If the instruction cannot be disassembled then an exception is thrown and the successors set is not modified.

Thread safety: The safety of this method depends on its implementation in the subclass. In any case, no other thread can be modifying the MemoryMap or successors set at the same time.

Implements Rose::BinaryAnalysis::Disassembler.

|

overridevirtual |

Makes an unknown instruction from an exception.

Thread safety: The safety of this method depends on its implementation in the subclass.

Implements Rose::BinaryAnalysis::Disassembler.

|

overridevirtual |

Unparser.

Returns an unparser suitable for unparsing the same instruction set architecture as recognized and produced by this disassembler.

Implements Rose::BinaryAnalysis::Disassembler.

| Mips32* Rose::BinaryAnalysis::DisassemblerMips::find_idis | ( | rose_addr_t | insn_va, |

| unsigned | insn_bits | ||

| ) | const |

Find an instruction-specific disassembler.

Using the specified instruction bits, search for and return an instruction-specific disassembler. Returns null if no appropriate disassembler can be found. Instruction-specific disassemblers know how to disassemble specific instruction types (or groups of closely related instructions).

| void Rose::BinaryAnalysis::DisassemblerMips::insert_idis | ( | Mips32 * | , |

| bool | replace = false |

||

| ) |

Insert an instruction-specific disassembler.

If replace is false (the default) then the table must not already contain an entry that has the same mask and match values. The pointers are managed by the caller and must not be deleted while they are in the table.

| SgAsmMipsInstruction* Rose::BinaryAnalysis::DisassemblerMips::disassemble_insn | ( | rose_addr_t | insn_va, |

| unsigned | insn_bits | ||

| ) | const |

Disassemble a single instruction.

Given the bits of a MIPS32 instruction, attempt to disassemble the instruction. If the bits can be disassembled, then a new SgAsmMipsInstruction is returned, otherwise it returns the null pointer. It may also throw an exception if a valid instruction-specific disassembler can be found but the instruction is malformed.

| SgAsmMipsInstruction* Rose::BinaryAnalysis::DisassemblerMips::makeInstruction | ( | rose_addr_t | insn_va, |

| MipsInstructionKind | , | ||

| const std::string & | mnemonic, | ||

| SgAsmExpression * | arg1 = NULL, |

||

| SgAsmExpression * | arg2 = NULL, |

||

| SgAsmExpression * | arg3 = NULL, |

||

| SgAsmExpression * | arg4 = NULL |

||

| ) | const |

Create a new instruction.

| SgAsmRegisterReferenceExpression* Rose::BinaryAnalysis::DisassemblerMips::makeRegister | ( | rose_addr_t | insn_va, |

| unsigned | regnum | ||

| ) | const |

Create a new general purpose register reference expression.

| SgAsmRegisterReferenceExpression* Rose::BinaryAnalysis::DisassemblerMips::makeFpRegister | ( | rose_addr_t | insn_va, |

| unsigned | regnum | ||

| ) | const |

Create a new floating point register reference expression.

| SgAsmRegisterReferenceExpression* Rose::BinaryAnalysis::DisassemblerMips::makeCp0Register | ( | rose_addr_t | insn_va, |

| unsigned | regnum, | ||

| unsigned | sel | ||

| ) | const |

Create a new register reference for Coprocessor 0.

| SgAsmRegisterReferenceExpression* Rose::BinaryAnalysis::DisassemblerMips::makeCp2Register | ( | unsigned | regnum | ) | const |

Create a new register reference for Coprocessor 2.

| SgAsmRegisterReferenceExpression* Rose::BinaryAnalysis::DisassemblerMips::makeFpccRegister | ( | rose_addr_t | insn_va, |

| unsigned | cc | ||

| ) | const |

Create a new floating point condition flag register reference expression.

The return value is a reference to one of the bits from the FCSR register. If cc is zero then bit 23 is referenced, otherwise bit 24+cc is referenced. The cc value must be zero through seven, inclusive.

| SgAsmRegisterReferenceExpression* Rose::BinaryAnalysis::DisassemblerMips::makeCp2ccRegister | ( | unsigned | cc | ) | const |

Create a new register reference for a COP2 condition code.

See COP2ConditionCode() in the MIPS reference manual.

| SgAsmRegisterReferenceExpression* Rose::BinaryAnalysis::DisassemblerMips::makeHwRegister | ( | unsigned | regnum | ) | const |

Create a new register reference for a hardware register.

See the RDHWR instruction documentation.

| SgAsmRegisterReferenceExpression* Rose::BinaryAnalysis::DisassemblerMips::makeShadowRegister | ( | rose_addr_t | insn_va, |

| unsigned | regnum | ||

| ) | const |

Create a new register reference for a shadow GPR.

| SgAsmIntegerValueExpression* Rose::BinaryAnalysis::DisassemblerMips::makeImmediate8 | ( | unsigned | value, |

| size_t | bit_offset, | ||

| size_t | nbits | ||

| ) | const |

Create a new 8-bit value expression from an 8-bit value.

The bit_offset and nbits indicate where the value originally came from in the instruction.

| SgAsmIntegerValueExpression* Rose::BinaryAnalysis::DisassemblerMips::makeImmediate16 | ( | unsigned | value, |

| size_t | bit_offset, | ||

| size_t | nbits | ||

| ) | const |

Create a new 16-bit value expression from a 16-bit value.

The bit_offset and nbits indicate where the value originally came from in the instruction.

| SgAsmIntegerValueExpression* Rose::BinaryAnalysis::DisassemblerMips::makeImmediate32 | ( | unsigned | value, |

| size_t | bit_offset, | ||

| size_t | nbits | ||

| ) | const |

Create a new 32-bit value expression from a 32-bit value.

The bit_offset and nbits indicate where the value originally came from in the instruction.

| SgAsmIntegerValueExpression* Rose::BinaryAnalysis::DisassemblerMips::makeBranchTargetRelative | ( | rose_addr_t | insn_va, |

| unsigned | offset16, | ||

| size_t | bit_offset, | ||

| size_t | nbits | ||

| ) | const |

Create a 32-bit PC-relative branch target address from a 16-bit offset.

The bit_offset and nbits indicate where the value originally came from in the instruction (usually 0 and 16, respectively). The return address is the address of the delay slot plus four times the signed offset16.

| SgAsmIntegerValueExpression* Rose::BinaryAnalysis::DisassemblerMips::makeBranchTargetAbsolute | ( | rose_addr_t | insn_va, |

| unsigned | insn_index, | ||

| size_t | bit_offset, | ||

| size_t | nbits | ||

| ) | const |

Create a 32-bit branch address from an instruction index value.

The returned value is the insn_index (nbits wide) multiplied by four and then combined with the address of the delay slot. They are combined such that the low-order nbits+2 bits are from the product and the upper bits are from the delay slot address.

| SgAsmBinaryAdd* Rose::BinaryAnalysis::DisassemblerMips::makeRegisterOffset | ( | rose_addr_t | insn_va, |

| unsigned | gprnum, | ||

| unsigned | offset16 | ||

| ) | const |

Build an expression for an offset from a register.

The return value is GPR[regnum]+signExtend(offset) expressed as an SgAsmBinaryAdd expression whose first operand is the register reference expression and second operand is the sign-extended offset.

| SgAsmBinaryAdd* Rose::BinaryAnalysis::DisassemblerMips::makeRegisterIndexed | ( | rose_addr_t | insn_va, |

| unsigned | base_gprnum, | ||

| unsigned | index_gprnum | ||

| ) | const |

Build a register index expression.

The returned value is makeRegister(base_gprnum)+makeRegister(index_gprnum).

| SgAsmMemoryReferenceExpression* Rose::BinaryAnalysis::DisassemblerMips::makeMemoryReference | ( | SgAsmExpression * | addr, |

| SgAsmType * | type | ||

| ) | const |

Build a memory reference expression.

Member Data Documentation

|

protected |

Table of instruction-specific disassemblers.

This is the table of instruction-specific disassemblers consulted by find_idis().

Definition at line 141 of file DisassemblerMips.h.

The documentation for this class was generated from the following file:

1.8.10

1.8.10