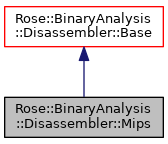

Description

MIPS32 instruction decoder.

MIPS (Microprocessor without Interlocked Pipelined Stages) is a family of reduced instruction set computer (RISC) instruction set architectures (ISA) developed by MIPS Computer Systems, now MIPS Technologies, based in the United States.

There are multiple versions of MIPS: including MIPS I, II, III, IV, and V; as well as five releases of MIPS32/64 (for 32- and 64-bit implementations, respectively). The early MIPS architectures were 32-bit; 64-bit versions were developed later. As of April 2017, the current version of MIPS is MIPS32/64 Release 6. MIPS32/64 primarily differs from MIPS I–V by defining the privileged kernel mode System Control Coprocessor in addition to the user mode architecture.

The MIPS architecture has several optional extensions. MIPS-3D which is a simple set of floating-point SIMD instructions dedicated to common 3D tasks, MDMX (MaDMaX) which is a more extensive integer SIMD instruction set using the 64-bit floating-point registers, MIPS16e which adds compression to the instruction stream to make programs take up less room, and MIPS MT, which adds multithreading capability.

The first release of MIPS32, based on MIPS II, added conditional moves, prefetch instructions, and other features from the R4000 and R5000 families of 64-bit processors. The MUL and MADD (multiply-add) instructions, previously available in some implementations, were added to the MIPS32 specifications, as were cache control instructions. For the purpose of cache control, both SYNC and SYNCI instructions were prepared.

Definition at line 37 of file Disassembler/Mips.h.

#include <Rose/BinaryAnalysis/Disassembler/Mips.h>

Classes | |

| class | Decoder |

| Interface for disassembling a single instruction. More... | |

Public Types | |

| using | Ptr = MipsPtr |

| Reference counting pointer. | |

Public Types inherited from Rose::BinaryAnalysis::Disassembler::Base Public Types inherited from Rose::BinaryAnalysis::Disassembler::Base | |

| using | Ptr = BasePtr |

Public Member Functions | |

| virtual Base::Ptr | clone () const override |

| Creates a new copy of a disassembler. | |

| virtual SgAsmInstruction * | disassembleOne (const MemoryMap::Ptr &, Address start_va, AddressSet *successors=NULL) override |

| This is the lowest level disassembly function and is implemented in the architecture-specific subclasses. | |

| virtual size_t | nDelaySlots (MipsInstructionKind) |

| virtual SgAsmInstruction * | makeUnknownInstruction (const Exception &) override |

| Makes an unknown instruction from an exception. | |

| SgAsmMipsInstruction * | makeUnknownInstruction (Address insn_va, unsigned opcode) const |

| Decoder * | find_idis (Address insn_va, unsigned insn_bits) const |

| Find an instruction-specific disassembler. | |

| void | insert_idis (Decoder *, bool replace=false) |

| Insert an instruction-specific disassembler. | |

| SgAsmMipsInstruction * | disassemble_insn (Address insn_va, unsigned insn_bits, const std::vector< uint8_t > &bytes) const |

| Disassemble a single instruction. | |

| SgAsmMipsInstruction * | makeInstruction (Address insn_va, MipsInstructionKind, SgAsmExpression *arg1=NULL, SgAsmExpression *arg2=NULL, SgAsmExpression *arg3=NULL, SgAsmExpression *arg4=NULL) const |

| Create a new instruction. | |

| SgAsmType * | makeType (MipsDataFormat) const |

| Create a ROSE type form a MIPS data format. | |

| SgAsmRegisterReferenceExpression * | makeRegister (Address insn_va, unsigned regnum) const |

| Create a new general purpose register reference expression. | |

| SgAsmRegisterReferenceExpression * | makeFpRegister (Address insn_va, unsigned regnum, MipsDataFormat) const |

| Create a new floating point register reference expression. | |

| SgAsmRegisterReferenceExpression * | makeCp0Register (Address insn_va, unsigned regnum, unsigned sel) const |

| Create a new register reference for Coprocessor 0. | |

| SgAsmRegisterReferenceExpression * | makeCp2Register (unsigned regnum) const |

| Create a new register reference for Coprocessor 2. | |

| SgAsmRegisterReferenceExpression * | makeFpccRegister (Address insn_va, unsigned cc) const |

| Create a new floating point condition flag register reference expression. | |

| SgAsmRegisterReferenceExpression * | makeCp2ccRegister (unsigned cc) const |

| Create a new register reference for a COP2 condition code. | |

| SgAsmRegisterReferenceExpression * | makeHwRegister (unsigned regnum) const |

| Create a new register reference for a hardware register. | |

| SgAsmRegisterReferenceExpression * | makeShadowRegister (Address insn_va, unsigned regnum) const |

| Create a new register reference for a shadow GPR. | |

| SgAsmIntegerValueExpression * | makeImmediate8 (unsigned value, size_t bit_offset, size_t nbits) const |

| Create a new 8-bit value expression from an 8-bit value. | |

| SgAsmIntegerValueExpression * | makeImmediate16 (unsigned value, size_t bit_offset, size_t nbits) const |

| Create a new 16-bit value expression from a 16-bit value. | |

| SgAsmIntegerValueExpression * | makeImmediate32 (unsigned value, size_t bit_offset, size_t nbits) const |

| Create a new 32-bit value expression from a 32-bit value. | |

| SgAsmIntegerValueExpression * | makeBranchTargetRelative (Address insn_va, unsigned offset16, size_t bit_offset, size_t nbits) const |

| Create a 32-bit PC-relative branch target address from a 16-bit offset. | |

| SgAsmIntegerValueExpression * | makeBranchTargetAbsolute (Address insn_va, unsigned insn_index, size_t bit_offset, size_t nbits) const |

| Create a 32-bit branch address from an instruction index value. | |

| SgAsmBinaryAdd * | makeRegisterOffset (Address insn_va, unsigned gprnum, unsigned offset16) const |

| Build an expression for an offset from a register. | |

| SgAsmBinaryAdd * | makeRegisterIndexed (Address insn_va, unsigned base_gprnum, unsigned index_gprnum) const |

| Build a register index expression. | |

| SgAsmMemoryReferenceExpression * | makeMemoryReference (SgAsmExpression *addr, SgAsmType *type) const |

| Build a memory reference expression. | |

Public Member Functions inherited from Rose::BinaryAnalysis::Disassembler::Base Public Member Functions inherited from Rose::BinaryAnalysis::Disassembler::Base | |

| Architecture::BaseConstPtr | architecture () const |

| Property: Architecture. | |

| virtual const std::string & | name () const |

| Property: Name. | |

| virtual size_t | bytesPerWord () const |

| Property: Bytes per word for the architecture. | |

| virtual ByteOrder::Endianness | byteOrder () const |

| Property: Byte order of memory. | |

| Unparser::BasePtr | unparser () const |

| Unparser. | |

| size_t | instructionAlignment () const |

| Property: Instruction alignment requirement. | |

| SgAsmInstruction * | disassembleOne (const unsigned char *buf, Address buf_va, size_t buf_size, Address start_va, AddressSet *successors=NULL) |

| Similar in functionality to the disassembleOne method that takes a MemoryMap argument, except the content buffer is mapped 1:1 to virtual memory beginning at the specified address. | |

| void | mark_referenced_instructions (SgAsmInterpretation *, const MemoryMap::Ptr &, const InstructionMap &) |

| Marks parts of the file that correspond to instructions as having been referenced. | |

| AddressSet | get_block_successors (const InstructionMap &, bool &complete) |

| Calculates the successor addresses of a basic block and adds them to a successors set. | |

| size_t | wordSizeBytes () const |

| RegisterDictionaryPtr | registerDictionary () const |

| virtual RegisterDescriptor | instructionPointerRegister () const |

| virtual RegisterDescriptor | stackPointerRegister () const |

| virtual RegisterDescriptor | stackFrameRegister () const |

| virtual RegisterDescriptor | stackSegmentRegister () const |

| virtual RegisterDescriptor | callReturnRegister () const |

Public Member Functions inherited from Sawyer::SharedObject Public Member Functions inherited from Sawyer::SharedObject | |

| SharedObject () | |

| Default constructor. | |

| SharedObject (const SharedObject &) | |

| Copy constructor. | |

| virtual | ~SharedObject () |

| Virtual destructor. | |

| SharedObject & | operator= (const SharedObject &) |

| Assignment. | |

Static Public Member Functions | |

| static Ptr | instance (const Architecture::BaseConstPtr &) |

| Allocating constructor for MIPS decoder. | |

Static Public Member Functions inherited from Rose::BinaryAnalysis::Disassembler::Base Static Public Member Functions inherited from Rose::BinaryAnalysis::Disassembler::Base | |

| static SgAsmInstruction * | find_instruction_containing (const InstructionMap &insns, Address va) |

| Finds the highest-address instruction that contains the byte at the specified virtual address. | |

Protected Member Functions | |

| Mips (const Architecture::BaseConstPtr &) | |

| void | init () |

Protected Member Functions inherited from Rose::BinaryAnalysis::Disassembler::Base Protected Member Functions inherited from Rose::BinaryAnalysis::Disassembler::Base | |

| Base (const Architecture::BaseConstPtr &) | |

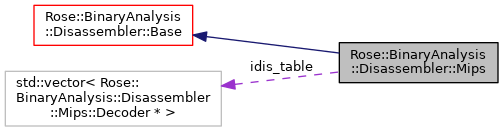

Protected Attributes | |

| std::vector< Decoder * > | idis_table |

| Table of instruction-specific disassemblers. | |

Protected Attributes inherited from Rose::BinaryAnalysis::Disassembler::Base Protected Attributes inherited from Rose::BinaryAnalysis::Disassembler::Base | |

| RegisterDescriptor | REG_IP |

| RegisterDescriptor | REG_SP |

| RegisterDescriptor | REG_SS |

| RegisterDescriptor | REG_SF |

| RegisterDescriptor | REG_LINK |

| Register descriptors initialized during construction. | |

| size_t | instructionAlignment_ = 1 |

| Positive alignment constraint for instruction addresses. | |

Member Typedef Documentation

◆ Ptr

Reference counting pointer.

Definition at line 40 of file Disassembler/Mips.h.

Member Function Documentation

◆ instance()

|

static |

Allocating constructor for MIPS decoder.

MIPS executables can be big- or little-endian.

◆ clone()

|

overridevirtual |

Creates a new copy of a disassembler.

The new copy has all the same settings as the original.

Thread safety: The thread safety of this virtual method depends on the implementation in the subclass.

Implements Rose::BinaryAnalysis::Disassembler::Base.

◆ disassembleOne()

|

overridevirtual |

This is the lowest level disassembly function and is implemented in the architecture-specific subclasses.

It disassembles one instruction at the specified virtual address. The map is a mapping from virtual addresses to buffer and enables instructions to span file segments that are mapped contiguously in virtual memory by the loader but which might not be contiguous in the file. The instruction's successor virtual addresses are added to the optional successor set (note that successors of an individual instruction can also be obtained via Architecture::Base::getSuccessors). If the instruction cannot be disassembled then an exception is thrown and the successors set is not modified.

Thread safety: The safety of this method depends on its implementation in the subclass. In any case, no other thread can be modifying the MemoryMap or successors set at the same time.

Implements Rose::BinaryAnalysis::Disassembler::Base.

◆ makeUnknownInstruction()

|

overridevirtual |

Makes an unknown instruction from an exception.

Thread safety: The safety of this method depends on its implementation in the subclass.

Implements Rose::BinaryAnalysis::Disassembler::Base.

◆ find_idis()

| Decoder * Rose::BinaryAnalysis::Disassembler::Mips::find_idis | ( | Address | insn_va, |

| unsigned | insn_bits | ||

| ) | const |

Find an instruction-specific disassembler.

Using the specified instruction bits, search for and return an instruction-specific disassembler. Returns null if no appropriate disassembler can be found. Instruction-specific disassemblers know how to disassemble specific instruction types (or groups of closely related instructions).

◆ insert_idis()

| void Rose::BinaryAnalysis::Disassembler::Mips::insert_idis | ( | Decoder * | , |

| bool | replace = false |

||

| ) |

Insert an instruction-specific disassembler.

If replace is false (the default) then the table must not already contain an entry that has the same mask and match values. The pointers are managed by the caller and must not be deleted while they are in the table.

◆ disassemble_insn()

| SgAsmMipsInstruction * Rose::BinaryAnalysis::Disassembler::Mips::disassemble_insn | ( | Address | insn_va, |

| unsigned | insn_bits, | ||

| const std::vector< uint8_t > & | bytes | ||

| ) | const |

Disassemble a single instruction.

Given the bits of a MIPS32 instruction, attempt to disassemble the instruction. If the bits can be disassembled, then a new SgAsmMipsInstruction is returned, otherwise it returns the null pointer. It may also throw an exception if a valid instruction-specific disassembler can be found but the instruction is malformed.

◆ makeFpccRegister()

| SgAsmRegisterReferenceExpression * Rose::BinaryAnalysis::Disassembler::Mips::makeFpccRegister | ( | Address | insn_va, |

| unsigned | cc | ||

| ) | const |

Create a new floating point condition flag register reference expression.

The return value is a reference to one of the bits from the FCSR register. If cc is zero then bit 23 is referenced, otherwise bit 24+cc is referenced. The cc value must be zero through seven, inclusive.

◆ makeCp2ccRegister()

| SgAsmRegisterReferenceExpression * Rose::BinaryAnalysis::Disassembler::Mips::makeCp2ccRegister | ( | unsigned | cc | ) | const |

Create a new register reference for a COP2 condition code.

See COP2ConditionCode() in the MIPS reference manual.

◆ makeHwRegister()

| SgAsmRegisterReferenceExpression * Rose::BinaryAnalysis::Disassembler::Mips::makeHwRegister | ( | unsigned | regnum | ) | const |

Create a new register reference for a hardware register.

See the RDHWR instruction documentation.

◆ makeImmediate8()

| SgAsmIntegerValueExpression * Rose::BinaryAnalysis::Disassembler::Mips::makeImmediate8 | ( | unsigned | value, |

| size_t | bit_offset, | ||

| size_t | nbits | ||

| ) | const |

Create a new 8-bit value expression from an 8-bit value.

The bit_offset and nbits indicate where the value originally came from in the instruction.

◆ makeImmediate16()

| SgAsmIntegerValueExpression * Rose::BinaryAnalysis::Disassembler::Mips::makeImmediate16 | ( | unsigned | value, |

| size_t | bit_offset, | ||

| size_t | nbits | ||

| ) | const |

Create a new 16-bit value expression from a 16-bit value.

The bit_offset and nbits indicate where the value originally came from in the instruction.

◆ makeImmediate32()

| SgAsmIntegerValueExpression * Rose::BinaryAnalysis::Disassembler::Mips::makeImmediate32 | ( | unsigned | value, |

| size_t | bit_offset, | ||

| size_t | nbits | ||

| ) | const |

Create a new 32-bit value expression from a 32-bit value.

The bit_offset and nbits indicate where the value originally came from in the instruction.

◆ makeBranchTargetRelative()

| SgAsmIntegerValueExpression * Rose::BinaryAnalysis::Disassembler::Mips::makeBranchTargetRelative | ( | Address | insn_va, |

| unsigned | offset16, | ||

| size_t | bit_offset, | ||

| size_t | nbits | ||

| ) | const |

Create a 32-bit PC-relative branch target address from a 16-bit offset.

The bit_offset and nbits indicate where the value originally came from in the instruction (usually 0 and 16, respectively). The return address is the address of the delay slot plus four times the signed offset16.

◆ makeBranchTargetAbsolute()

| SgAsmIntegerValueExpression * Rose::BinaryAnalysis::Disassembler::Mips::makeBranchTargetAbsolute | ( | Address | insn_va, |

| unsigned | insn_index, | ||

| size_t | bit_offset, | ||

| size_t | nbits | ||

| ) | const |

Create a 32-bit branch address from an instruction index value.

The returned value is the insn_index (nbits wide) multiplied by four and then combined with the address of the delay slot. They are combined such that the low-order nbits+2 bits are from the product and the upper bits are from the delay slot address.

◆ makeRegisterOffset()

| SgAsmBinaryAdd * Rose::BinaryAnalysis::Disassembler::Mips::makeRegisterOffset | ( | Address | insn_va, |

| unsigned | gprnum, | ||

| unsigned | offset16 | ||

| ) | const |

Build an expression for an offset from a register.

The return value is GPR[regnum]+signExtend(offset) expressed as an SgAsmBinaryAdd expression whose first operand is the register reference expression and second operand is the sign-extended offset.

◆ makeRegisterIndexed()

| SgAsmBinaryAdd * Rose::BinaryAnalysis::Disassembler::Mips::makeRegisterIndexed | ( | Address | insn_va, |

| unsigned | base_gprnum, | ||

| unsigned | index_gprnum | ||

| ) | const |

Build a register index expression.

The returned value is makeRegister(base_gprnum)+makeRegister(index_gprnum).

Member Data Documentation

◆ idis_table

|

protected |

Table of instruction-specific disassemblers.

This is the table of instruction-specific disassemblers consulted by find_idis().

Definition at line 172 of file Disassembler/Mips.h.

The documentation for this class was generated from the following file: